计算机组成原理2

存储器(重点)

概述

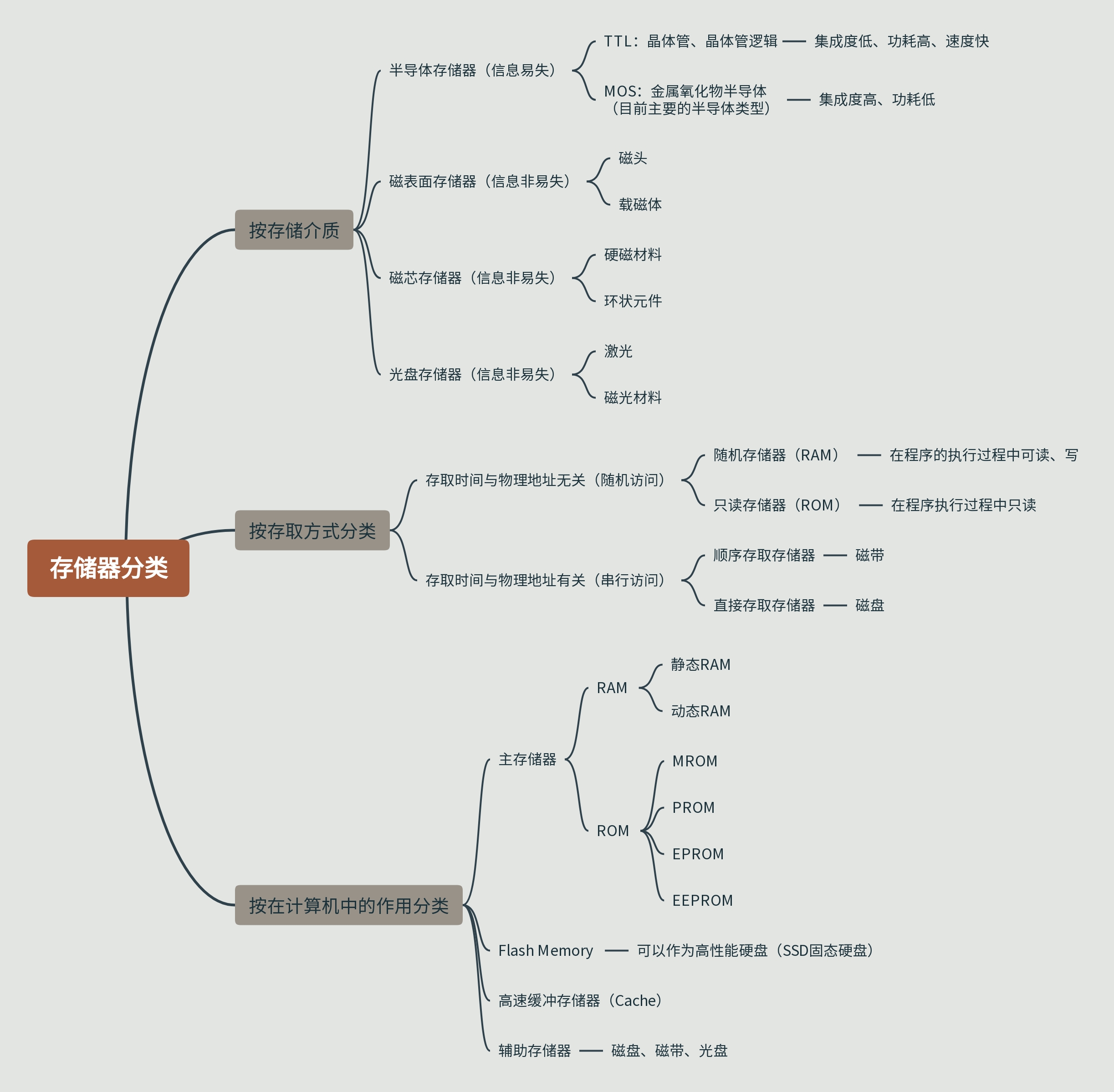

存储器分类

存储器的层次结构

-

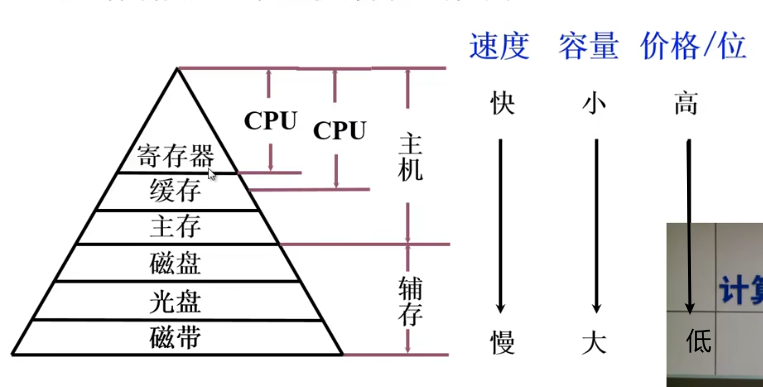

存储体系:把两种或两种以上的存储介质构成的存储器,用软件、硬件或者软硬件相结合将其连接成一个整体,使得从某一级程序员角度看,这个整体具有高速、大容量、低价格的特点。

-

存储器三个主要特性的关系:

- 速度:速度越快,容量越小,价格越高

- 容量:容量越大,速度越慢,价格越低

- 价格:价格越高,容量越低,速度越快

- 计算机两个重要的存储层次

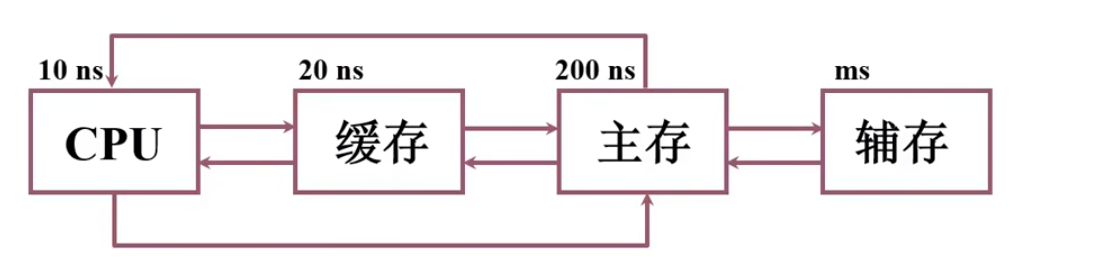

- 缓存-主存层次:为了解决CPU运算速率与主存存取速率差距越来越大的问题,引入了缓存(Cache),形成缓存-主存层次

- 主存-辅存层次

- 在构建这两个层次时运用到了程序的局部性原理:时间的局部性原理,空间的局部性

- 缓存-主存(偏向速度):更多依赖硬件管理(如 CPU 内部的缓存机制),但也有软件优化的部分。

- 主存-辅存(偏向容量):主要依赖软件(如操作系统的虚拟内存管理),硬件提供了基础的连接与传输能力。通常将主存和辅存构成的整体通常称为虚拟存储器

主存储器(重点)

概述

主存的基本组成

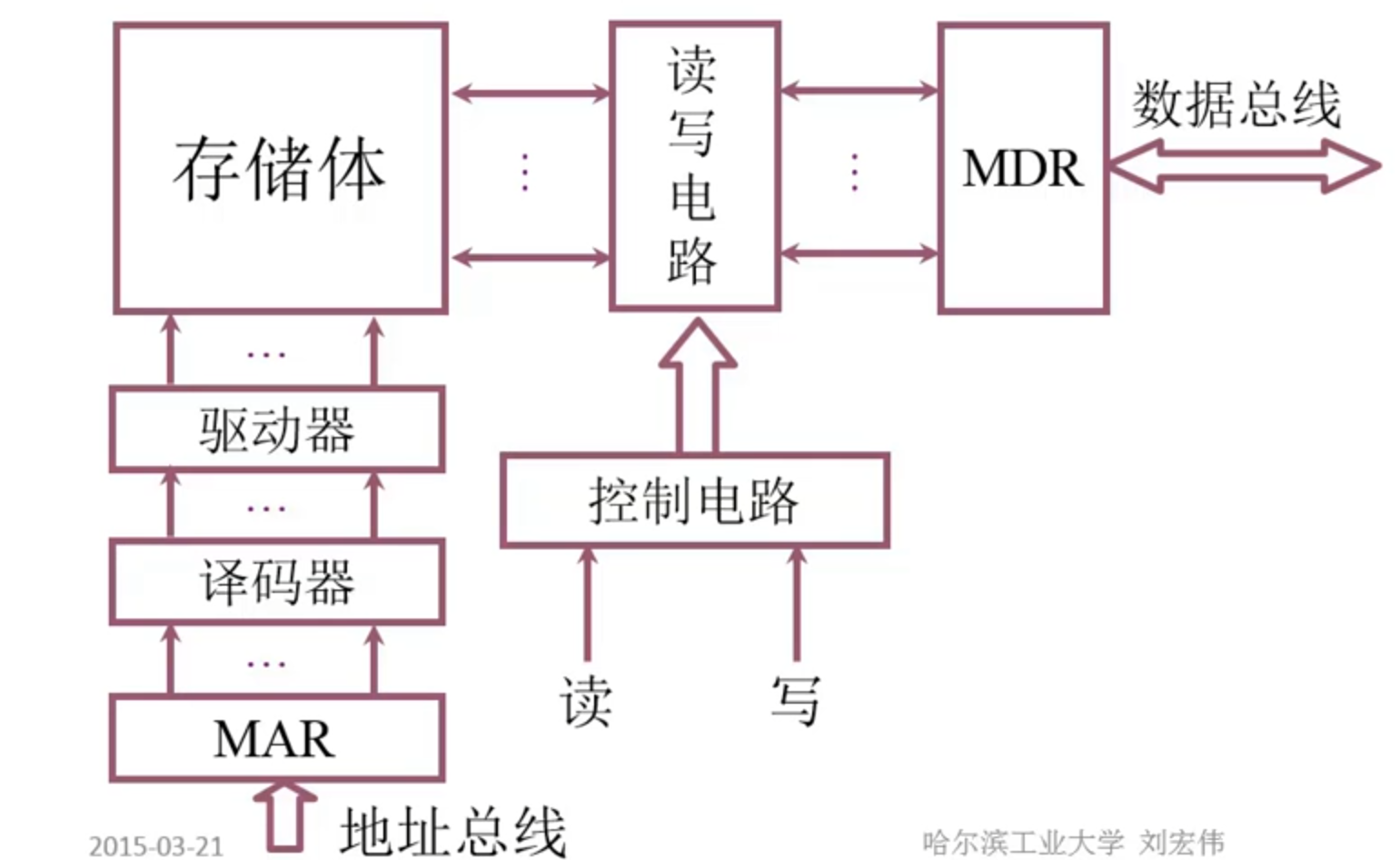

- 之前在概述的时候简化的主存结构为:存储体、MAR、MDR。

- 下图给出主存的基本组成

- MAR保存了将要访问的存储单元的地址,但是MAR要经过译码器进行译码以后才能选定指定的存储单元

- MDR保存了要读出或者写入的数据。具体是读还是写要根据读写电路判断。

- 读出,那么指定存储体里面的数据将会送入MDR。

- 写入,那么MDR里面的数据将会送入指定存储体里面。

- 也就是说控制电路,控制着读写电路的传输方向

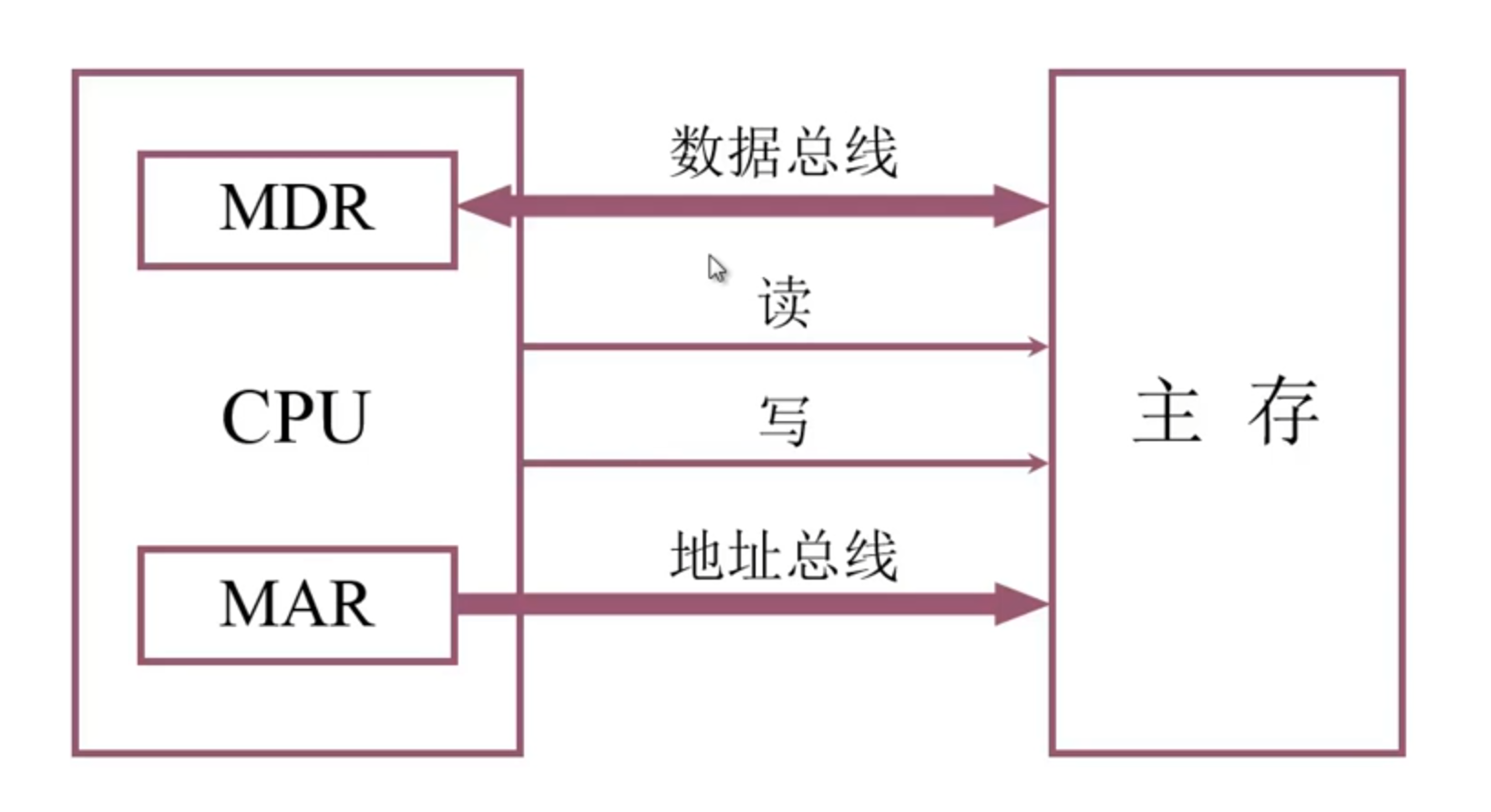

主存与CPU之间的联系

- CPU与主存之间的连接信号分成三类,数据、地址、控制总线(注:MAR和MDR逻辑上属于主存,物理上属于CPU)

- 数据总线:完成了CPU与主存之间的数据传输,数据总线直接连接在MDR寄存器上,是双向的

- 地址总线:连接在MAR寄存器和主存的地址总线之间,给出了要访问内存单元的地址,是单向的

- 控制信号这里给了两个读和写,实际上不只读和写

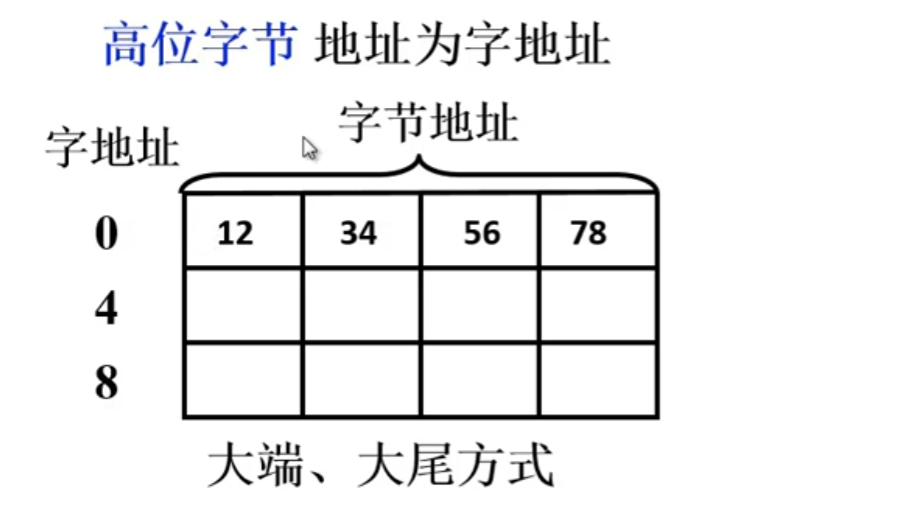

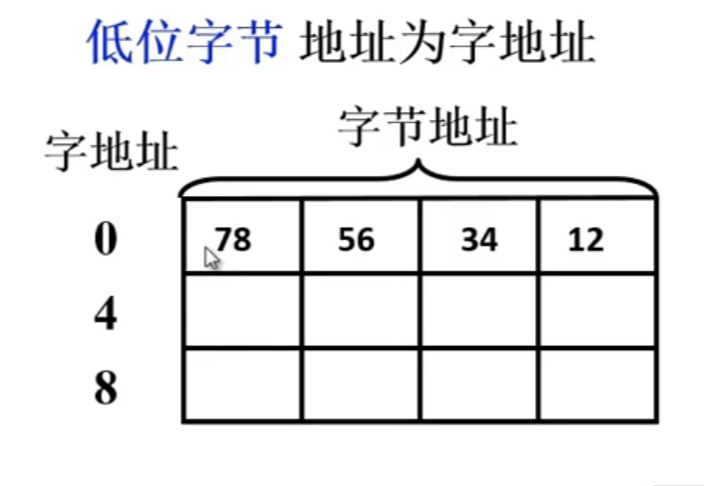

主存中存储单元地址的分配

-

这个部分不多解释,搞re和pwn对这个还是比较熟悉的

-

这个部分即存储数据的方式,该方式有两个,大端序和小端序。

-

x86架构的一般都是小端序,而在网络传输中一般都是大端序

-

大端序:高位字节放低地址,低位字节放高地址

- 小端序:低位放低地址,高位放高地址

- 设地址线24根,按字节寻址,24根地址线对每个字节都进行编址,则这个存储器容量为

16MB - 若字长位16位,按

字寻址,则存储器容量为8MW - 若字长位32位,地址线还是24根,按

字寻址,则存储器容量为4MW

主存的技术指标

- 存储容量:主存存放二进制代码的总位数

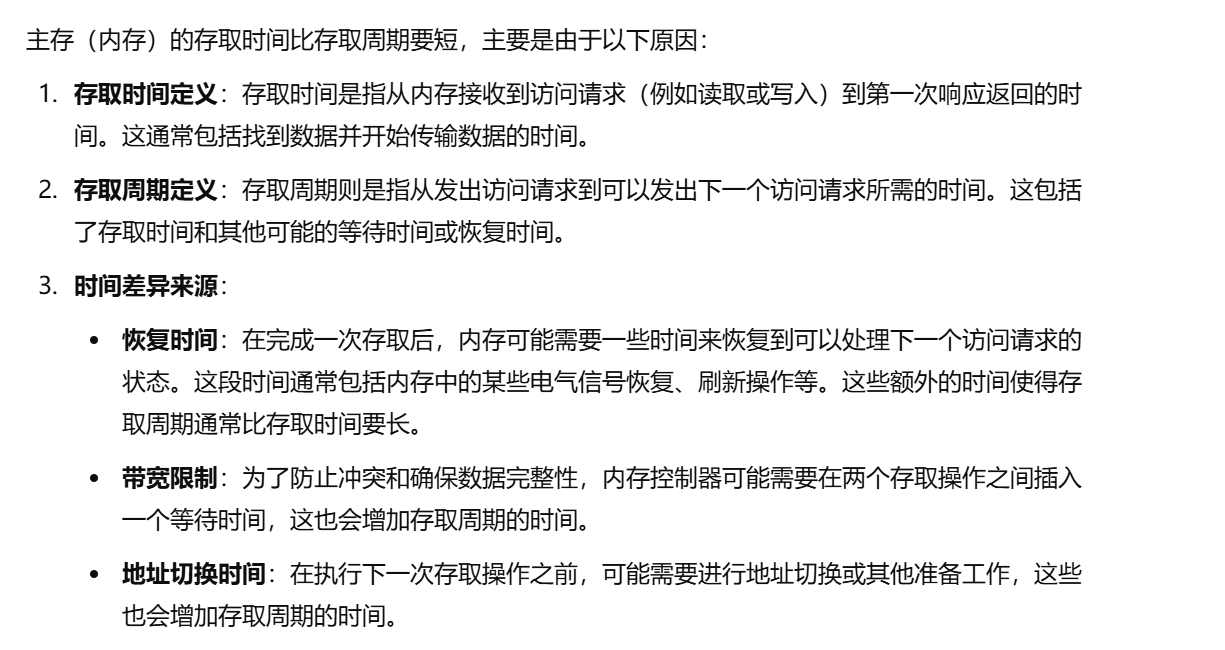

- 存储速度:

- 存取时间:存储器的访问时间,从存储器给出地址直到得到稳定的数据输出或数据输入,这个时间就是存储时间。还可以细分为

读出时间和写入时间 - 存取周期:连续两次独立的存储器操作(读或写)所需要的最小间隔时间。还可以细分为

读周期、写周期 - 一般来说存取周期要比存取时间要长

- 存取时间:存储器的访问时间,从存储器给出地址直到得到稳定的数据输出或数据输入,这个时间就是存储时间。还可以细分为

- 存储器的带宽(位/秒):单位时间能够读取或者能够向存储器写入的数据量

- 存取时间比存取周期短的原因

半导体芯片简介

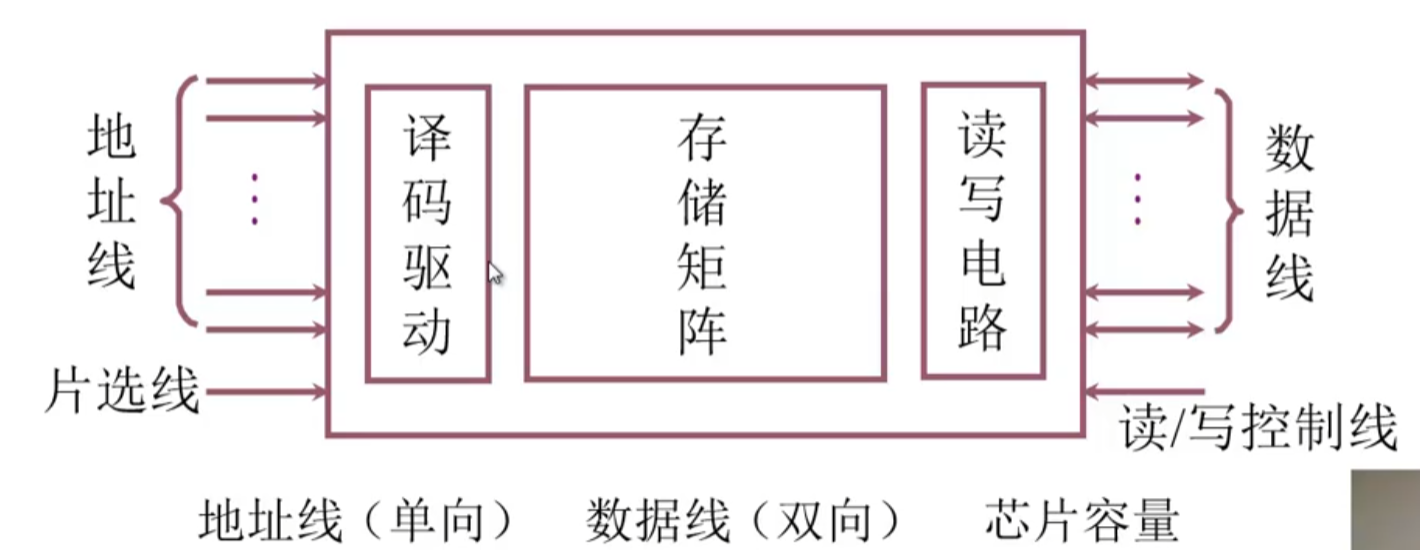

半导体存储芯片的基本结构

- 半导体存储芯片的基本结构如下:

- 核心部分:译码驱动器、存储矩阵、读写电路

- 连接部分:地址线、数据线、片选线、读/写控制线

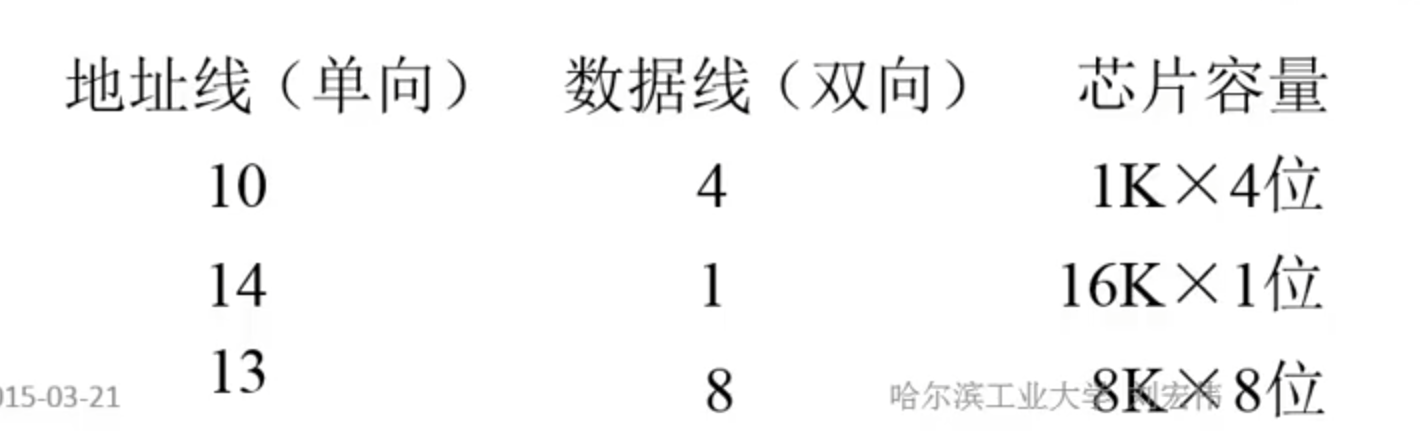

- 芯片容量

- 芯片的容量根据地址线和数据线:地址线为

m根、数据线为n根,那么芯片容量就为2^m * 2^n位

-

读写控制线:有的用一根线表示、有的用两个线表示

- 一根线时:WE(有效是写,无效是读)(还要看电路是低电平有效还是高电平有效)

- 当有两根线时还有一根线:OE(允许读操作)、WE(允许写操作)

-

片选线:访问哪个芯片中的数据,就是由片选线决定的

-

半导体片选线有两种标识方式:CS、CE

-

CS:芯片选择

-

CE:芯片使能

-

-

片选线的作用:可以让某个芯片或者某些芯片同时进行工作

-

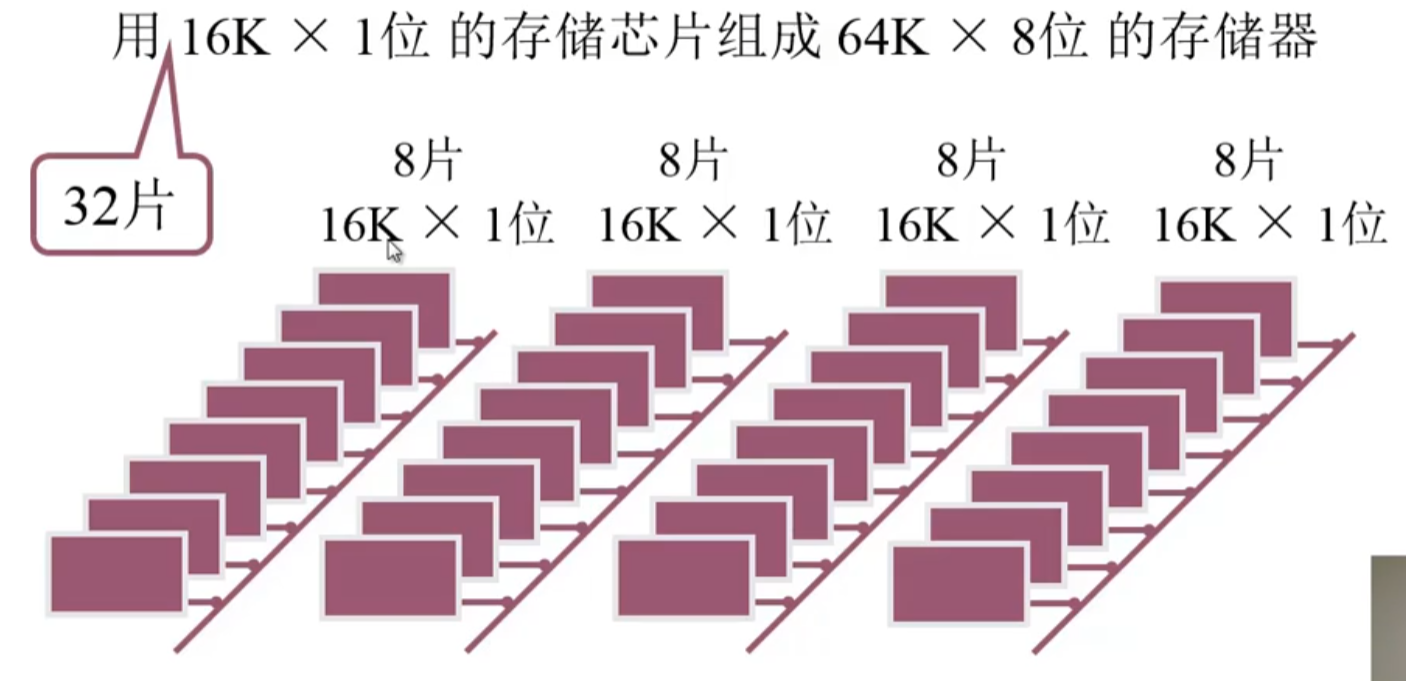

例如:当要用

16K * 1位的存储芯片组成64K * 8位的存储器时,如何读写相应的芯片组,这就是片选线要做的。这时存储芯片的布局如下- 每一束下来表示的是8位,把这8位看成一个整体,有4个16k的8为存储芯片,就构成了

64K * 8的存储器 - 使用片选线,将这些连接起来,并规定输入的地址线范围在

0~16K-1这个范围选择左边第一排的存储芯片。 - 第一排中的每个存储芯片都存或者取8位中的1位。这样就可以保证存储

8位。容量大小为64K

- 每一束下来表示的是8位,把这8位看成一个整体,有4个16k的8为存储芯片,就构成了

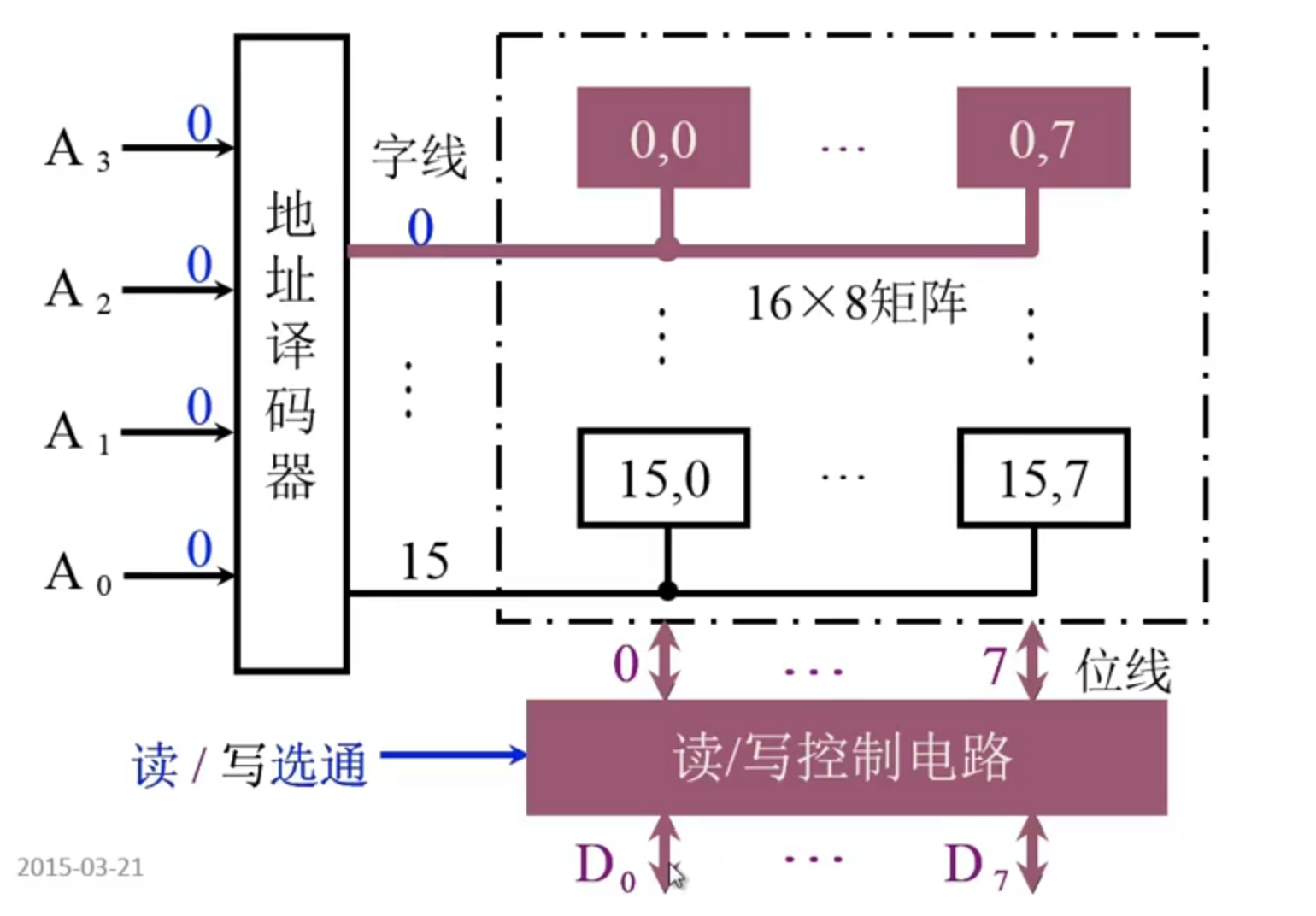

半导体存储芯片的译码驱动方式

- 该译码驱动方式分为:线选法、重合法

线选法

- 地址译码器:多输入单输出,输入是四根线,输出是十六根线

- 读写电路:控制读写的操作,从读写电路的线中可以看到1个内存单元存储

8位 - 16×8的矩阵:存储单元

- 具体过程:

- 地址译码器输出端输入信号,选择内存读写的内存单元

- 地址译码器输出端就会使得其中一根线有效,即选中某个内存单元

- 读写控制电路,控制其进行读操作

- 被选中的内存单元数据被读出来,传输到指定设备中

- 缺点:地址译码器的输出线需要非常多,将其做入芯片中也非常密集,集成度也不高

重合法

高速缓冲存储器

辅助存储器

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 iyheart的博客!